The most common types of reliability tests for semiconductors are; burn-in, power temp cycle (PTC), and HAST.

Burn-in

Burn-in tests check the reliability of the semiconductor device and are typically done at 125ºC or 150ºC, while electrical signals and power are applied to ASICs. Burn-in boards are put into the burn-in system which supplies the necessary power and stimulus to the samples while maintaining the oven temperature at the required temperature. After the stress testing, the samples must be tested on ATE to ensure they passed the oven testing.

PTC

Power and temperature cycle testing, (PTC) is performed to determine the ability of a device to withstand alternate exposures at high and low-temperature extremes with operating biases periodically applied and removed.

HAST

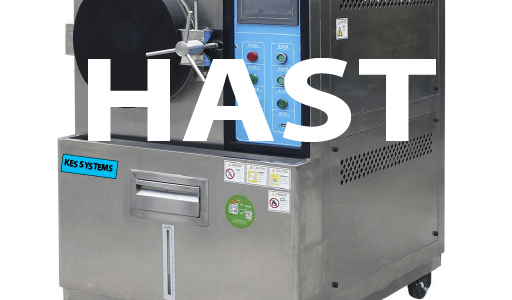

HAST stands for Highly Accelerated Temperature/Humidity Stress Test and is shortened to Highly Accelerated Stress Testing. HAST uses accelerated temperature and humidity conditions to precipitate failures which could be caused by long term exposure to humid environments.

HAST was developed to replace Temperature-Humidity-Bias (THB) testing. THB has typical conditions of 85 ⁰C and 85 % RH along with a bias voltage applied to the sample. A typical THB test time would be 1000 hours. HAST uses increased test temperatures of 110 to 130 ⁰C which decreases the test time to 96 hours typically. Thus, by choosing HAST over THB for an accelerated reliability test, testing can finish in days, not weeks.

HAST utilizes a positive pressure inside the test chamber (usually 2 to 3 atmospheres) along with temperatures above 100 ⁰C and controlled humidity. This requires that the chamber be tightly sealed to prevent leaks. Testing is performed with or without a voltage bias on the samples.

For a biased test, a DC voltage is applied to the samples. For semiconductors, the samples are placed in sockets located inside the test chamber. Wires inside of the chamber pass through a sealed feed-through where they are connected to power supplies located outside of the chamber. The bias can be continuous or cyclic DC voltage.

Common standards used for HAST are JESD22-A110, JESD22-A118, IEC 60068-2-66.

The purpose of HAST is to evaluate a device’s resistance to humidity by increasing the water vapor pressure in the HAST chamber. This process temporarily accelerates the infiltration of moisture into the device under test (DUT).

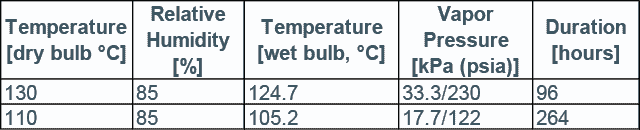

Typical test conditions are:

HAST is considered by most semiconductor manufacturers to be a fast and reliable alternative to THB and is an important part of package qualifications. At KES, we design and build HAST boards for all platforms, including Despatch, Delta V, Reltech, Hirayama, and others.

For more information and to learn how KES Systems can help you with your HAST, burn-in, or other test needs, please contact us.